# DS64EV100 Programmable Single Equalizer

### **General Description**

The DS64EV100 programmable equalizer provides compensation for transmission medium losses and reduces the medium-induced deterministic jitter for NRZ data channel. The DS64EV100 is optimized for operation up to 10 Gbps for both cables and FR4 traces. The equalizer channel has eight levels of input equalization that can be programmed by three control pins.

The equalizer supports both AC and DC-coupled data paths for long run length data patterns such as PRBS-31, and balanced codes such as 8b/10b. The device uses differential current-mode logic (CML) inputs and outputs. The DS64EV100 is available in a 3 mm x 4 mm 14-pin leadless LLP package. Power is supplied from either a 2.5V or 3.3V supply.

### **Features**

- Equalizes up to 24 dB loss at 10 Gbps

- Equalizes up to 22 dB loss at 6.4 Gbps

- 8 levels of programmable equalization

- Operates up to 10 Gbps with 30" FR4 traces

- Operates up to 6.4 Gbps with 40" FR4 traces

- 0.175 UI residual deterministic jitter at 6.4 Gbps with 40" FR4 traces

- Single 2.5V or 3.3V power supply

- Supports AC or DC-Coupling with wide input commonmode

- Low power consumption: 100 mW Typ at 2.5V

- Small 3 mm x 4 mm 14-pin LLP package

- > 8 kV HBM ESD Rating

- -40 to 85°C operating temperature range

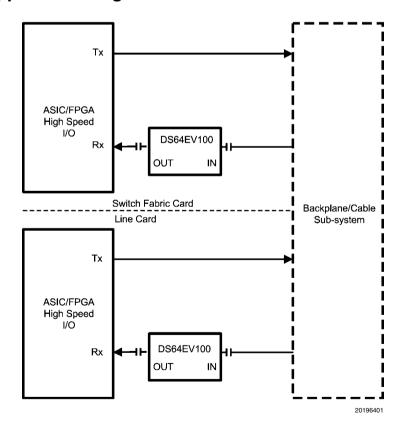

### **Simplified Application Diagram**

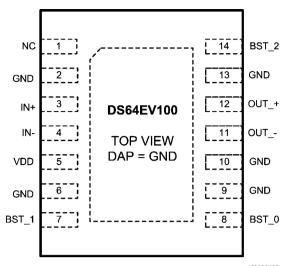

# **Pin Diagram**

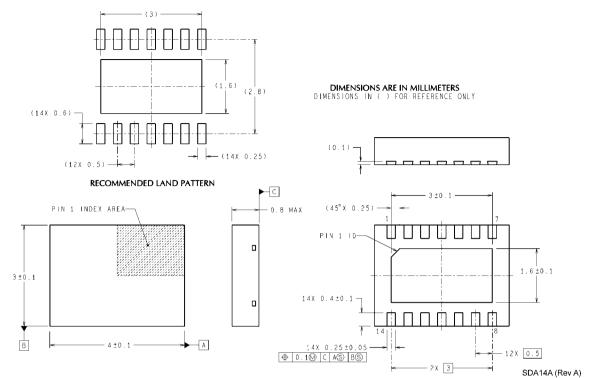

14-Pin LLP Package (3 mm x 4 mm x 0.8 mm, 0.5 mm pitch) See NS Package Number SQA14A

# **Ordering Information**

| NSID         | Package Type, Qty Size                                       | Package ID |

|--------------|--------------------------------------------------------------|------------|

| DS64EV100SD  | 14-pin LLP (3 mm x 4 mm x 0.8 mm, 0.5 mm pitch, reel of 1000 | SDA14A     |

| DS64EV100SDX | 14-pin LLP (3 mm x 4 mm x 0.8 mm, 0.5 mm pitch, reel of 4500 | SDA14A     |

## **Pin Descriptions**

| Pin Name                | Pin #                       | I/O,<br>Type | Description                                                                                                                                                                                          |  |  |  |

|-------------------------|-----------------------------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| HIGH SPEED              | HIGH SPEED DIFFERENTIAL I/O |              |                                                                                                                                                                                                      |  |  |  |

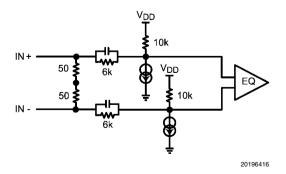

| IN+<br>IN-              | 3<br>4                      | I, CML       | Inverting and non-inverting CML differential inputs to the equalizer. An on-chip $100\Omega$ terminating resistor is connected between IN+ and IN Refer to Figure 4.                                 |  |  |  |

| OUT+<br>OUT-            | 12<br>11                    | O, CML       | Inverting and non-inverting CML differential outputs from the equalizer. An on-chip $50\Omega$ terminating resistor connects OUT+ to $V_{DD}$ and OUT- to $V_{DD}$ .                                 |  |  |  |

| EQUALIZATI              | ON CONTRO                   | L .          |                                                                                                                                                                                                      |  |  |  |

| BST_2<br>BST_1<br>BST_0 | 14<br>7<br>8                | I, CMOS      | BST_2, BST_1, and BST_0 select the equalizer strength. BST_2 is internally pulled high. BST_1 and BST_0 are internally pulled low.                                                                   |  |  |  |

| POWER                   |                             | !            |                                                                                                                                                                                                      |  |  |  |

| V <sub>DD</sub>         | 5                           | I, Power     | $V_{DD}$ = 2.5V ±5% or 3.3V ±10%. $V_{DD}$ pins should be tied to $V_{DD}$ plane through low inductance path. A 0.01µF bypass capacitor should be connected between each $V_{DD}$ pin to GND planes. |  |  |  |

| GND                     | 2, 6, 9, 10,<br>13          | I, Power     | Ground reference. GND should be tied to a solid ground plane through a low impedance path.                                                                                                           |  |  |  |

| DAP                     | PAD                         | I, Power     | Ground reference. The exposed pad at the center of the package must be connected to ground plane of the board.                                                                                       |  |  |  |

| OTHER                   |                             |              |                                                                                                                                                                                                      |  |  |  |

| NC                      | 1                           |              | Reserved. Do not connect.                                                                                                                                                                            |  |  |  |

Note: I = Input, O = Output

## **Absolute Maximum Ratings** (Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

If Military/Aerospace specified devices are required, please contact the National Semiconductor sales offices/ distributors for availability and specifications.

| Supply Voltage (V <sub>DD</sub> ) | -0.5V to +4V     |

|-----------------------------------|------------------|

| CMOS Input Voltage                | -0.5V to $+4.0V$ |

| CMOS Output Voltage               | -0.5V to +4.0V   |

| CML Input/Output Voltage          | -0.5V to $+4.0V$ |

| Junction Temperature              | +150°C           |

| Storage Temperature               | -65°C to +150°C  |

| Lead Temperature                  |                  |

| Soldering, 4 sec                  | +260°C           |

ESD Rating  $\begin{array}{ll} \text{HBM, 1.5 k}\Omega, \, 100 \, \text{pF} & > 8 \, \text{kV} \\ \text{EIAJ, 0}\Omega, \, 200 \, \text{pF} & > 250 \, \text{V} \\ \text{Thermal Resistance, } \theta_{\text{JA}}, & & & \\ \text{No Airflow} & & 40 \, ^{\circ}\text{C/W} \end{array}$

# **Recommended Operating Conditions**

|                           | Min   | Тур | Max   | Units |

|---------------------------|-------|-----|-------|-------|

| Supply Voltage (Note 9)   |       |     |       |       |

| V <sub>DD2.5</sub> to GND | 2.375 | 2.5 | 2.625 | ٧     |

| V <sub>DD3.3</sub> to GND | 3.0   | 3.3 | 3.6   | ٧     |

| Ambient Temperature       | -40   | 25  | +85   | °C    |

### **Electrical Characteristics**

Over recommended operating supply and temperature ranges unless other specified. (Notes 2, 3)

| Symbol                  | Parameter                                           | Conditions                                                                            | Min                    | Typ<br>(Note 2) | Max                    | Units             |

|-------------------------|-----------------------------------------------------|---------------------------------------------------------------------------------------|------------------------|-----------------|------------------------|-------------------|

| POWER                   | •                                                   |                                                                                       | •                      | •               |                        |                   |

| Р                       | Power Supply                                        | V <sub>DD3.3</sub>                                                                    |                        | 140             | 200                    | mW                |

|                         | Consumption                                         | $V_{DD2.5}$                                                                           |                        | 100             | 150                    | mW                |

| N                       | Supply Noise                                        | 50 Hz – 100 Hz                                                                        |                        | 100             |                        | mV <sub>P-P</sub> |

|                         | Tolerance (Note 4)                                  | 100 Hz – 10 MHz                                                                       |                        | 40              |                        | $mV_{P-P}$        |

|                         |                                                     | 10 MHz – 1.6 GHz                                                                      |                        | 10              |                        | $mV_{P-P}$        |

| LVTTL DC                | SPECIFICATIONS                                      |                                                                                       |                        | •               |                        |                   |

| V <sub>IH</sub>         | High Level Input                                    | V <sub>DD2.5</sub>                                                                    | 1.6                    |                 | V <sub>DD2.5</sub>     | V                 |

|                         | Voltage                                             | V <sub>DD3.3</sub>                                                                    | 2.0                    |                 | V <sub>DD3.3</sub>     | V                 |

| V <sub>IL</sub>         | Low Level Input<br>Voltage                          |                                                                                       | -0.3                   |                 | 0.8                    | V                 |

| V <sub>OH</sub>         | High Level Output                                   | $I_{OH} = -3 \text{ mA}, V_{DD3.3}$                                                   | 2.4                    |                 |                        | V                 |

|                         | Voltage                                             | $I_{OH} = -3 \text{ mA}, V_{DD2.5}$                                                   | 2.0                    |                 |                        | V                 |

| V <sub>OL</sub>         | Low Level Output<br>Voltage                         | I <sub>OL</sub> = 3 mA                                                                |                        |                 | 0.4                    | V                 |

| I <sub>IN</sub> Input   | Input Current                                       | $V_{IN} = V_{DD}$                                                                     |                        | +1.8            | +15                    | μA                |

|                         |                                                     | V <sub>IN</sub> = GND                                                                 | -15                    | 0               |                        | μΑ                |

| I <sub>IN-P</sub> Input | Input Leakage                                       | V <sub>IN</sub> = GND, with internal pull-down resistors                              |                        | +95             |                        | μΑ                |

|                         | Current with Internal<br>Pull-Down/Up<br>Resistors  | V <sub>IN</sub> = GND, with internal pull-up resistors                                | -20                    |                 |                        | μA                |

| CML REC                 | EIVER INPUTS (IN+, IN                               | l-)                                                                                   |                        |                 |                        |                   |

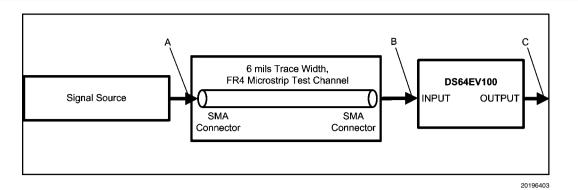

| V <sub>TX</sub>         | Source Transmit<br>Launch Signal Level<br>(IN diff) | AC-Coupled or DC-Coupled Requirement, Differential measurement at point A. (Figure 1) | 400                    |                 | 1600                   | $mV_{P-P}$        |

| V <sub>INTRE</sub>      | Input Threshold<br>Voltage                          | Differential measurement at point B . (Figure 1)                                      |                        | 120             |                        | mV <sub>P-P</sub> |

| V <sub>DDTX</sub>       | Supply Voltage of<br>Transmitter to EQ              | DC-Coupled Requirement                                                                | 1.6                    |                 | V <sub>DD</sub>        | V                 |

| V <sub>ICMDC</sub>      | Input Common-Mode<br>Voltage                        | DC-Coupled Requirement Differential measurement at point A. (Figure 1), (Note 7)      | V <sub>DDTX</sub> -0.8 |                 | V <sub>DDTX</sub> -0.2 | V                 |

| Symbol                          | Parameter                                          | Conditions                                                                                                   | Min                  | Typ<br>(Note 2) | Max                  | Units             |

|---------------------------------|----------------------------------------------------|--------------------------------------------------------------------------------------------------------------|----------------------|-----------------|----------------------|-------------------|

| R <sub>LI</sub>                 | Differential Input<br>Return Loss                  | 100 MHz – 3.2 GHz, with fixture's effect de-                                                                 |                      | 10              |                      | dB                |

| R <sub>IN</sub>                 | Input Resistance                                   | Differential Across IN+ and IN (Figure 4)                                                                    | 85                   | 100             | 115                  | Ω                 |

|                                 | PUTS (OUT+, OUT-)                                  | , , ,                                                                                                        |                      |                 |                      |                   |

| V <sub>OD</sub>                 | Output Differential<br>Voltage Level (OUT<br>diff) | Differential measurement with OUT+ and OUT-terminated by $50\Omega$ to GND, AC-Coupled (Figure 2)            | 550                  | 620             | 725                  | mV <sub>P-P</sub> |

| V <sub>OCM</sub>                | Output Common-<br>Mode Voltage                     | Single-ended measurement DC-Coupled with $50\Omega$ terminations (Note 7)                                    | V <sub>DD</sub> -0.2 |                 | V <sub>DD</sub> -0.1 | V                 |

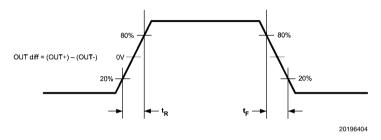

| t <sub>R</sub> , t <sub>F</sub> | Transition Time                                    | 20% to 80% of differential output voltage,<br>measured within 1" from output pins.<br>(Figure 2)<br>(Note 7) | 20                   |                 | 60                   | ps                |

| R <sub>O</sub>                  | Output Resistance                                  | Single-ended to V <sub>DD</sub>                                                                              | 42                   | 50              | 58                   | Ω                 |

| R <sub>LO</sub>                 | Differential Output<br>Return Loss                 | 100 MHz – 1.6 GHz, with fixture's effect de-<br>embedded. IN+ = static high.                                 |                      | 10              |                      | dB                |

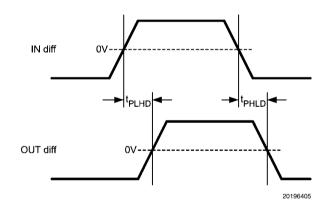

| t <sub>PLHD</sub>               | Differential Low to<br>High Propagation<br>Delay   | Propagation delay measurement at 50% V <sub>OD</sub> between input to output, 100 Mbps (Figure 3), (Note 7)  |                      | 240             |                      | ps                |

| t <sub>PHLD</sub>               | Differential High to<br>Low Propagation<br>Delay   |                                                                                                              |                      | 240             |                      | ps                |

| EQUALIZA                        | ATION                                              | <u>'</u>                                                                                                     |                      |                 |                      |                   |

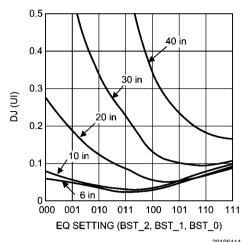

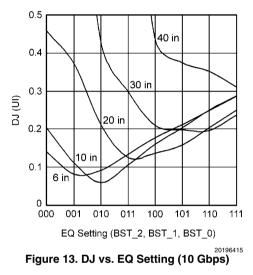

| DJ1                             | Residual<br>Deterministic Jitter at<br>10 Gbps     | 30" of 6 mil microstrip FR4, EQ Setting 0x06,<br>PRBS-7 (2 <sup>7</sup> -1) pattern<br>(Note 5, 6)           |                      | 0.20            |                      | UI <sub>P-P</sub> |

| DJ2                             | Residual Deterministic Jitter at 6.4 Gbps          | 40" of 6 mil microstrip FR4, EQ Setting 0x06, PRBS-7 (27-1) pattern (Note 5, 6)                              |                      | 0.17            | 0.26                 | UI <sub>P-P</sub> |

| DJ3                             | Residual Deterministic Jitter at 5 Gbps            | 40" of 6 mil microstrip FR4, EQ Setting 0x07, PRBS-7 (27-1) pattern (Note 5, 6)                              |                      | 0.12            | 0.20                 | UI <sub>P-P</sub> |

| DJ4                             | Residual Deterministic Jitter at 2.5 Gbps          | 40" of 6 mil microstrip FR4, EQ Setting 0x07,<br>PRBS-7 (2 <sup>7</sup> -1) pattern<br>(Note 5, 6)           |                      | 0.10            | 0.16                 | UI <sub>P-P</sub> |

| RJ                              | Random Jitter                                      | (Note 7, 8)                                                                                                  | _                    | 0.5             | _                    | ps <sub>rms</sub> |

**Note 1:** "Absolute Maximum Ratings" indicate limits beyond which damage to the device may occur, including inoperability and degradation of device reliability and/or performance. Functional operation of the device and/or non-degradation at the Absolute Maximum Ratings or other conditions beyond those indicated in the Recommended Operating Conditions is not implied. The Recommended Operating Conditions indicate conditions at which the device is functional and the device should not be operated beyond such conditions. Absolute Maximum Numbers are guaranteed for a junction temperature range of –40°C to +125°C. Models are validated to Maximum Operating Voltages only.

Note 2: Typical values represent most likely parametric norms at  $V_{DD} = 3.3V$  or 2.5V,  $T_A = 25^{\circ}C$ ., and at the Recommended Operation Conditions at the time of product characterization and are not guaranteed.

**Note 3:** The Electrical Characteristics tables list guaranteed specifications under the listed Recommended Operating Conditions except as otherwise modified or specified by the Electrical Characteristics Conditions and/or Notes. Typical specifications are estimations only and are not guaranteed.

- Note 4: Allowed supply noise (mV $_{\text{P-P}}$  sine wave) under typical conditions.

- Note 5: Specification is guaranteed by characterization at optimal boost setting and is not tested in production.

- **Note 6:** Deterministic jitter is measured at the differential outputs (point C of Figure 1), minus the deterministic jitter before the test channel (point A of Figure 1). Random jitter is removed through the use of averaging or similar means.

- Note 7: Measured with clock-like {11111 00000} pattern.

- **Note 8:** Random jitter contributed by the equalizer is defined as sqrt  $(J_{OUT}^2 J_{IN}^2)$ .  $J_{OUT}$  is the random jitter at equalizer outputs in ps<sub>rms</sub>, see point C of Figure 1;  $J_{IN}$  is the random jitter at the input of the equalizer in ps<sub>rms</sub>, see Figure 1.

- **Note 9:** The  $V_{DD2.5}$  is  $V_{DD} = 2.5V \pm 5\%$  and  $V_{DD3.3}$  is  $V_{DD} = 3.3V \pm 10\%$ .

FIGURE 1. Test Setup Diagram

**FIGURE 2. CML Output Transition Times**

FIGURE 3. Propagation Delay Timing Diagram

FIGURE 4. Simplified Receiver Input Termination Circuit

5

www.national.com

# DS64EV100 Applications Information

The DS64EV100 is a programmable equalizer optimized for operation up to 10 Gbps for backplane and cable applications.

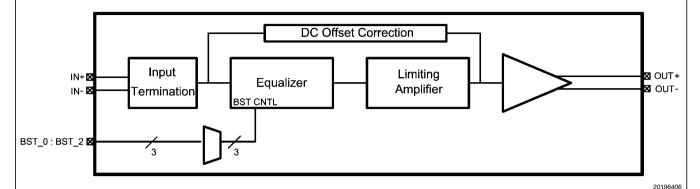

The equalizer channel consists of an equalizer stage, a limiting amplifier, a DC offset correction block, and a CML driver as shown in Figure 5.

FIGURE 5. Simplified Block Diagram

EQUALIZER BOOST CONTROL

The equalizer channel supports eight programmable levels of equalization boost, and is controlled by the Boost Set pins (BST\_[2:0]) in accordance with Table 1. The eight levels of boost settings enables the DS64EV100 to address a wide range of media loss and data rates.

**TABLE 1. EQ Boost Control Table**

| 6 mil<br>Microstri<br>p FR4<br>Trace<br>Length<br>(in) | 24 AWG<br>Twin-AX<br>Cable<br>Length<br>(m) | Channel<br>Loss at<br>3.2 GHz<br>(db) | Channel<br>Loss at 5<br>GHz (dB) | BST_N<br>[2, 1, 0] |

|--------------------------------------------------------|---------------------------------------------|---------------------------------------|----------------------------------|--------------------|

| 0                                                      | 0                                           | 0                                     | 0                                | 000                |

| 5                                                      | 2                                           | 5                                     | 6                                | 001                |

| 10                                                     | 3                                           | 7.5                                   | 10                               | 010                |

| 15                                                     | 4                                           | 10                                    | 14                               | 011                |

| 20                                                     | 5                                           | 12.5                                  | 18                               | 1 0 0<br>(Default) |

| 25                                                     | 6                                           | 15                                    | 21                               | 101                |

| 30                                                     | 7                                           | 17                                    | 24                               | 110                |

| 40                                                     | 10                                          | 22                                    | 30                               | 111                |

#### **GENERAL RECOMMENDATIONS**

The DS64EV100 is a high performance circuit capable of delivering excellent performance. Careful attention must be paid to the details associated with high-speed design as well as providing a clean power supply. Refer to the LVDS Owner's Manual for more detailed information on high-speed design tips to address signal integrity design issues.

# PCB LAYOUT CONSIDERATIONS FOR DIFFERENTIAL PAIRS

The CML inputs and outputs must have a controlled differential impedance of  $100\Omega$ . It is preferable to route CML lines

exclusively on one layer of the board, particularly for the input traces. The use of vias should be avoided if possible. If vias must be used, they should be used sparingly and must be placed symmetrically for each side of a given differential pair. Route the CML signals away from other signals and noise sources on the printed circuit board. See AN-1187 for additional information on LLP packages.

#### **POWER SUPPLY BYPASSING**

Two approaches are recommended to ensure that the DS64EV100 is provided with an adequate power supply. First, the supply (VDD) and ground (GND) pins should be connected to power planes routed on adjacent layers of the printed circuit board. The layer thickness of the dielectric should be minimized so that the  $V_{\rm DD}$  and GND planes create a low inductance supply with distributed capacitance. Second, careful attention to supply bypassing through the proper use of bypass capacitors is required. A 0.01µF bypass capacitor should be connected to each V<sub>DD</sub> pin such that the capacitor is placed as close as possible to the DS64EV100. Smaller body size capacitors can help facilitate proper component placement. Additionally, three capacitors with capacitance in the range of 2.2 µF to 10 µF should be incorporated in the power supply bypassing design as well. These capacitors can be either tantalum or an ultra-low ESR ceramic and should be placed as close as possible to the DS64EV100.

#### **DC COUPLING**

The DS64EV100 supports both AC coupling with external ac coupling capacitor, and DC coupling to its upstream driver, or downstream receiver. With DC coupling, users must ensure the input signal common mode is within the range of the electrical specification  $\rm V_{ICMDC}$  and the device output is terminated with 50  $\Omega$  to  $\rm V_{DD}$ .

www.national.com 6

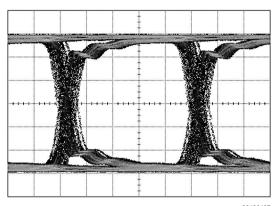

## **Typical Performance Eye Diagrams and Curves**

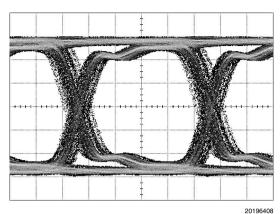

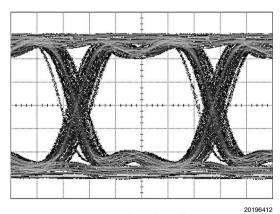

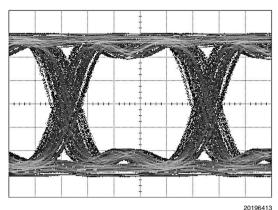

Figure 5. Equalized Signal (40 in FR4, 2.5 Gbps, PRBS7, 0x07 Setting)

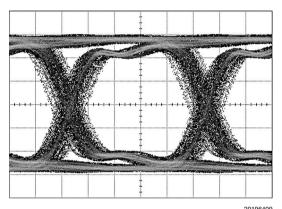

Figure 6. Equalized Signal (40 in FR4, 5 Gbps, PRBS7, 0x07 Setting)

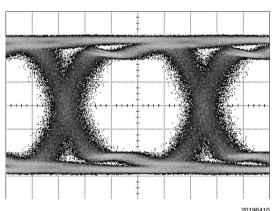

Figure 7. Equalized Signal (40 in FR4, 6.4 Gbps, PRBS7, 0x06 Setting)

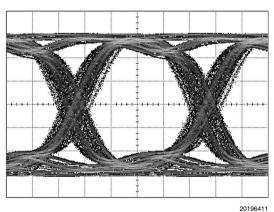

Figure 8. Equalized Signal (40 in FR4, 6.4 Gbps, PRBS31, 0x06 Setting)

Figure 9. Equalized Signal (30 in FR4, 10 Gbps, PRBS7, 0x06 Setting)

Figure 10. Equalized Signal (10m 24 AWG Twin-AX Cable, 6.4 Gbps, PRBS7, 0x06 Setting)

7

Figure 11. Equalized Signal (32 in Tyco XAUI Backplane, 6.25 Gbps, PRBS7, 0x06 Setting)

Figure 12. DJ vs. EQ Setting (6.4 Gbps)

8 www.national.com

## Physical Dimensions inches (millimeters) unless otherwise noted

14-Pin Leadless LLP Package (3 mm x 4 mm x 0.8 mm, 0.5 mm pitch) Order Number DS64EV100SD NS Package Number SDA14A

### **Notes**

For more National Semiconductor product information and proven design tools, visit the following Web sites at:

| Pr                             | oducts                       | Design Support          |                                |  |

|--------------------------------|------------------------------|-------------------------|--------------------------------|--|

| Amplifiers                     | www.national.com/amplifiers  | WEBENCH                 | www.national.com/webench       |  |

| Audio                          | www.national.com/audio       | Analog University       | www.national.com/AU            |  |

| Clock Conditioners             | www.national.com/timing      | App Notes               | www.national.com/appnotes      |  |

| Data Converters                | www.national.com/adc         | Distributors            | www.national.com/contacts      |  |

| Displays                       | www.national.com/displays    | Green Compliance        | www.national.com/quality/green |  |

| Ethernet                       | www.national.com/ethernet    | Packaging               | www.national.com/packaging     |  |

| Interface                      | www.national.com/interface   | Quality and Reliability | www.national.com/quality       |  |

| LVDS                           | www.national.com/lvds        | Reference Designs       | www.national.com/refdesigns    |  |

| Power Management               | www.national.com/power       | Feedback                | www.national.com/feedback      |  |

| Switching Regulators           | www.national.com/switchers   |                         |                                |  |

| LDOs                           | www.national.com/ldo         |                         |                                |  |

| LED Lighting                   | www.national.com/led         |                         |                                |  |

| PowerWise                      | www.national.com/powerwise   |                         |                                |  |

| Serial Digital Interface (SDI) | www.national.com/sdi         |                         |                                |  |

| Temperature Sensors            | www.national.com/tempsensors |                         |                                |  |

| Wireless (PLL/VCO)             | www.national.com/wireless    |                         |                                |  |

THE CONTENTS OF THIS DOCUMENT ARE PROVIDED IN CONNECTION WITH NATIONAL SEMICONDUCTOR CORPORATION ("NATIONAL") PRODUCTS. NATIONAL MAKES NO REPRESENTATIONS OR WARRANTIES WITH RESPECT TO THE ACCURACY OR COMPLÉTENESS OF THE CONTENTS OF THIS PUBLICATION AND RESERVES THE RIGHT TO MAKE CHANGES TO SPECIFICATIONS AND PRODUCT DESCRIPTIONS AT ANY TIME WITHOUT NOTICE. NO LICENSE, WHETHER EXPRESS, IMPLIED, ARISING BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT.

TESTING AND OTHER QUALITY CONTROLS ARE USED TO THE EXTENT NATIONAL DEEMS NECESSARY TO SUPPORT NATIONAL'S PRODUCT WARRANTY. EXCEPT WHERE MANDATED BY GOVERNMENT REQUIREMENTS, TESTING OF ALL PARAMETERS OF EACH PRODUCT IS NOT NECESSARILY PERFORMED. NATIONAL ASSUMES NO LIABILITY FOR APPLICATIONS ASSISTANCE OR BUYER PRODUCT DESIGN. BUYERS ARE RESPONSIBLE FOR THEIR PRODUCTS AND APPLICATIONS USING NATIONAL COMPONENTS. PRIOR TO USING OR DISTRIBUTING ANY PRODUCTS THAT INCLUDE NATIONAL COMPONENTS, BUYERS SHOULD PROVIDE ADEQUATE DESIGN, TESTING AND OPERATING SAFEGUARDS

EXCEPT AS PROVIDED IN NATIONAL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS. NATIONAL ASSUMES NO LIABILITY WHATSOEVER, AND NATIONAL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY RELATING TO THE SALE AND/OR USE OF NATIONAL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS PRIOR WRITTEN APPROVAL OF THE CHIEF EXECUTIVE OFFICER AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

Life support devices or systems are devices which (a) are intended for surgical implant into the body, or (b) support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in a significant injury to the user. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system or to affect its safety or effectiveness.

National Semiconductor and the National Semiconductor logo are registered trademarks of National Semiconductor Corporation. All other brand or product names may be trademarks or registered trademarks of their respective holders.

Copyright© 2008 National Semiconductor Corporation

For the most current product information visit us at www.national.com

National Semiconductor Americas Technical Support Center Email: new.feedback@nsc.com

**Technical Support Center** Email: europe.support@nsc.com German Tel: +49 (0) 180 5010 771 English Tel: +44 (0) 870 850 4288 Tel: 1-800-272-9959

National Semiconductor Europe

National Semiconductor Asia Pacific Technical Support Center Email: ap.support@nsc.com

National Semiconductor Japan **Technical Support Center** Email: jpn.feedback@nsc.com